# CONVERSIONE ANALOGICA DIGITALE (ADC) (A/D) CONVERSIONE DIGITALE ANALOGICA (DAC) (D/A)

# ELABORAZIONE ANALOGICA O DIGITALE DEI SEGNALI

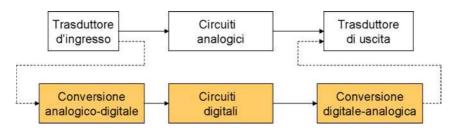

# ELABORAZIONE ANALOGICA

ELABORAZIONE DIGITALE

Vantaggi dell'elaborazione digitale:

- > Minore sensibilità ai disturbi

- > Elaborazione più semplice e meno costosa

- > Maggiore versatilità

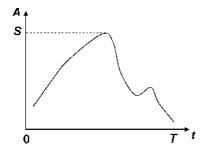

Una grandezza analogica può assumere qualunque valore all'interno di un dato intervallo 0-S (continua in ampiezza) ed è definita in ogni istante di tempo in un determinato intervallo 0-T (continua in tempo)

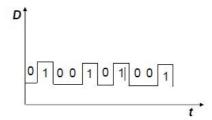

Una grandezza numerica (o digitale) è una lista di numeri che rappresentano il segnale analogico in determinati istanti (discreta in tempo). Dato che un numero con N cifre con base 2 può rappresentare  $2^N$  valori, una grandezza numerica rappresenta solo un numero finito di valori all'interno dell'intervallo 0-S (discreta in ampiezza)

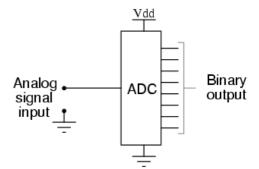

Quindi in generale è frequente è la necessità di convertire un segnale analogico in digitale (convertitore ADC) e quello digitale in analogico (convertitore DAC).

Un segnale analogico posto in ingresso di un convertitore ADC è convertito in uscita in un numero binario. In un diagramma a blocchi si ha:

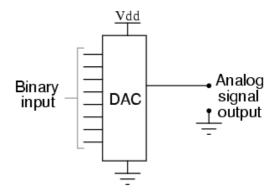

D'altra parte un convertitore digitale analogico (DAC), converte in un segnale analogico un numero binario in ingresso. In un diagramma a blocchi si ha:

Entrambi i convertitori vengono spesso utilizzati nei sistemi digitali come interfacce di ingresso tra sensori analogici e sistema di controllo elettronico digitale, e interfacce di uscita tra il sistema di controllo e i dispositivi di uscita.

# CONVERSIONE ANALOGICO-DIGITALE

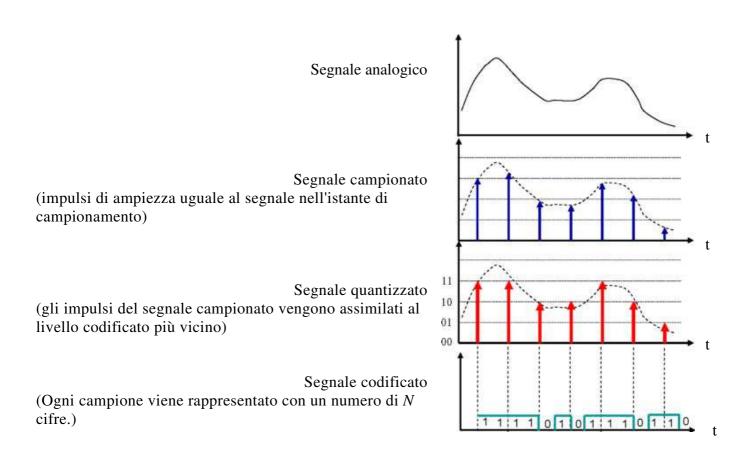

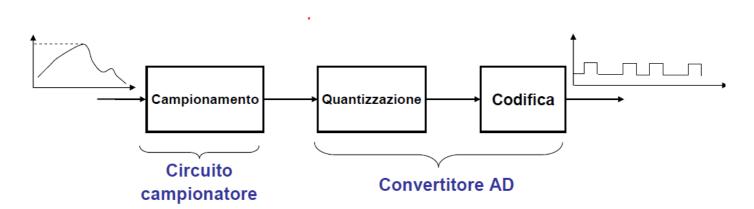

La conversione da analogico a digitale richiede tre operazioni:

Campionamento discretizzazione in tempo Quantizzazione discretizzazione in ampiezza

Codifica rappresentazione del campione quantizzato con un numero di N cifre

#### **CAMPIONAMENTO**

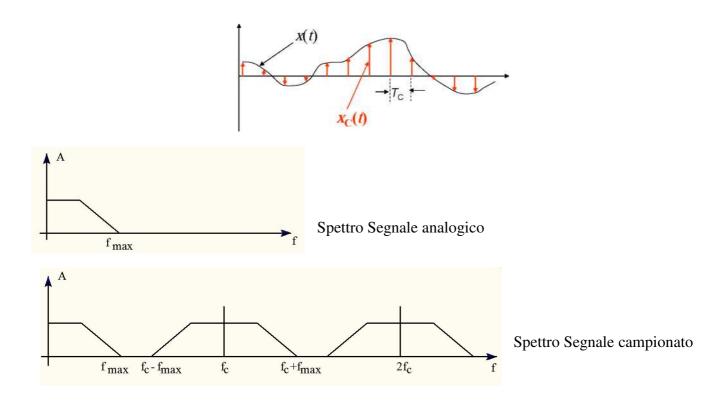

L'operazione di campionamento trasforma un segnale analogico x(t) in una sequenza di segnali impulsivi, di ampiezza uguale al valore del segnale originario ad istanti di tempo determinati.

IL segnale campionato  $x_C(t)$  si ottiene moltiplicando il segnale analogico per una serie di  $\delta$  di Dirac

$f_C = 1/T_C$ : frequenza di campionamento

Per ricostruire il segnale originario x(t) è sufficiente isolare mediante un filtro passa-basso la parte di spettro in banda base ma questo è possibile solo se le diverse bande non si sovrappongono.

La frequenza 2f<sub>max</sub> è chiamata frequenza di Nyquist

In elettronica e telecomunicazioni il **teorema del campionamento** è uno dei teoremi base della teoria dei segnali e mette in relazione il contenuto di un segnale campionato con la frequenza di campionamento e le componenti minime e massime di frequenza del segnale analogico originale, definendo così la minima frequenza necessaria per campionare un segnale analogico senza perdere informazioni e per poter quindi ricostruire il segnale analogico tempo continuo originario, detta **frequenza di Nyquist** o **cadenza di Nyquist**.

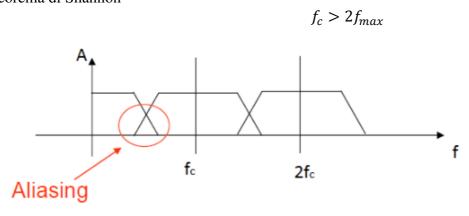

Teorema di Shannon

se il teorema non è rispettato si ha il fenomeno di aliasing che rende impossibile riottenere il segnale originale senza distorsioni.

Nessun segnale reale è a banda rigorosamente limitata, per cui si inserisce un filtro detto antialiasing prima del circuito campionatore.

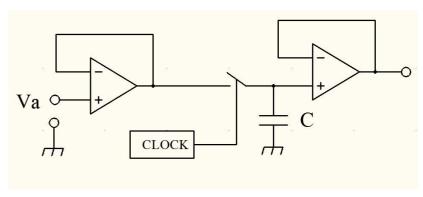

# IL CIRCUITO SAMPLE AND HOLD

L'operazione di conversione A/D non è istantanea, occorre quindi mantenere il valore del campione per il tempo necessario ad eseguire la conversione. Questa operazione viene eseguita mediante un circuito di sample/hold (campionamento e mantenimento).

Quando chiudiamo l'interruttore (fase sample) il condensatore si carica idealmente in un tempo nullo essendo nulla la resistenza di carica data dalla serie della resistenza d'uscita dell'operazionale e dalla resistenza dell'interruttore. Quindi il tempo di carica 5RC idealmente è zero.

Quando apriamo l'interruttore (fase hold)

il condensatore non si scarica perchè vede solo l'ingresso dell'operazionale a resistenza idealmente infinita.

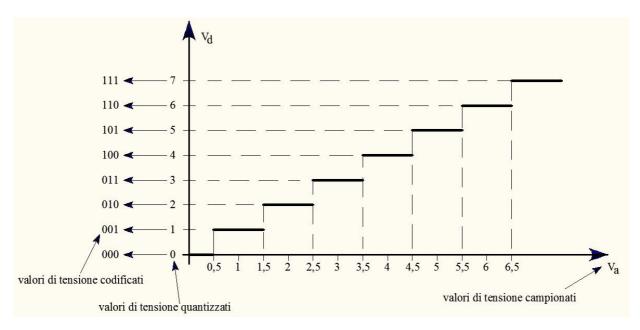

# Caratteristica ideale di un convertitore ADC

Facciamo l'esempio per un convertitore un convertitore ADC a 3 Bit, N numero di bit

V<sub>fs</sub> valore di fondo scala, praticamente il range d'ingresso del ADC

$\epsilon_{0}$

$$Q = \frac{\bar{V}_{fs}}{2^N}$$

$V_{\text{max}}$  valore discreto massimo  $V_{\text{max}} = V_{fs} - Q$

errore di quantizzazione massimo  $\varepsilon_Q = \frac{Q}{2}$

Nel nostro semplice esempio N=3  $V_{fs}$ =8V Q=1V  $V_{max}$ =7V  $\varepsilon_Q = \frac{1}{2}V$

Se aumentiamo il numero di bit

Se V<sub>fs</sub>=8V N=8 Q=31,25mV V<sub>max</sub>=7,96875V

$$\varepsilon_0$$

= 15,625 $mV$

Quindi il numero di bit definisce la risoluzione del nostro convertitore

Nella pratica, la risoluzione di un convertitore è limitata dal rapporto segnale/rumore (*S/N ratio*) del segnale in questione. Se è presente troppo rumore all'ingresso analogico, sarà impossibile convertire con accuratezza oltre un certo numero di bit di risoluzione. Anche se l'ADC produrrà un valore, questo non sarà accurato essendo i bit meno significativi funzione del rumore e non del segnale. Il rapporto S/N dovrebbe essere di circa 6 dB per bit.

# CODIFICA

# Codici unipolari pesati e non pesati

- Codice binario puro E' il codice normalmente usato per valori positivi.

- Codice BCD E' usato principalmente negli strumenti di misura.

- Codice di Gray E' un esempio di codice non pesato. Ogni codice differisce dal successivo di un bit. E' usato raramente.

| Valore    | Binario | BCD 8421 |      | Codice  |

|-----------|---------|----------|------|---------|

| per S= 15 | puro    |          |      | di Gray |

| 0         | 0000    |          | 0000 | 0000    |

| 1         | 0001    |          | 0001 | 0001    |

| 2         | 0010    |          | 0010 | 0011    |

| 3         | 0011    |          | 0011 | 0010    |

| 4         | 0100    |          | 0100 | 0110    |

| 5         | 0101    |          | 0101 | 0111    |

| 6         | 0110    |          | 0110 | 0101    |

| 7         | 0111    |          | 0111 | 0100    |

| 8         | 1000    |          | 1000 | 1100    |

| 9         | 1001    |          | 1001 | 1101    |

| 10        | 1010    | 0001     | 0000 | 1111    |

| 11        | 1011    | 0001     | 0001 | 1110    |

| 12        | 1100    | 0001     | 0010 | 1010    |

| 13        | 1101    | 0001     | 0011 | 1011    |

| 14        | 1110    | 0001     | 0100 | 1001    |

| 15        | 1111    | 0001     | 0101 | 1000    |

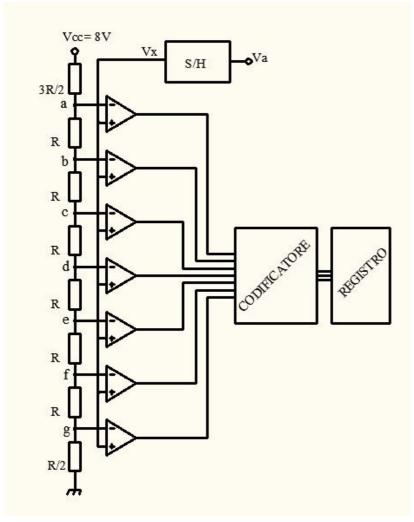

# **CONVERTITORE ADC FLASH**

tensione di confronto 0,5V, in f la tensione 1,5V e così via.

Un **ADC** a conversione diretta (*Flash ADC*) ha un comparatore per ognuno dei livelli di voltaggio riconosciuti dal quantizzatore.

Nel nostro esempio ADC flash a 3-bit avrà  $2^3$ -1 = 8-1 comparatori. Il segnale di ingresso arriva a tutti i comparatori. Porteranno in uscita un valore di saturazione positivo (livello logico 1) tutti quelli in cui la tensione del segnale di ingresso è maggiore di quella di soglia per quel determinato bit, gli altri comparatori avranno in uscita valore 0 (livello logico 0). Attraverso un priority encoder solo il maggiore di essi attiverà la propria uscita, quello del livello corrispondente (vedi tabella sottostante). I convertitori flash sono i più veloci in assoluto e sono usati per campionare segnali in alta frequenza, fino a diversi GHz. Poiché il numero di comparatori necessari cresce esponenzialmente con il numero dei bit richiesti (2<sup>N</sup>-1), i convertitori flash raramente hanno più di 8 bit di risoluzione.

In figura ci rifacciamo alla caratteristica disegnata a 3 bit. Nel punto g in figura c'e la

# CODIFICATORE CON PRIORITA'

| C7          | C6   | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | $C_2$ | C <sub>1</sub> | $a_2$ | $a_1$ | <i>a</i> <sub>0</sub> |

|-------------|------|----------------|----------------|----------------|-------|----------------|-------|-------|-----------------------|

| 0           | 0    | 0              | 0              | 0              | 0     | 0              | 0     | 0     | 0                     |

| 0           | 0    | 0              | 0              | 0              | 0     | 1              | 0     | 0     | 1                     |

| 0           | 0    | 0              | 0              | 0              | 1     | X              | 0     | 1     | 0                     |

| 0           | 0    | 0              | 0              | 1              | x     | x              | 0     | 1     | 1                     |

| 0           | 0    | 0              | 1              | х              | x     | x              | 1     | 0     | 0                     |

| 0           | 0    | 1              | x              | х              | x     | x              | 1     | 0     | 1                     |

| 0           | 1    | x              | x              | X              | x     | x              | 1     | 1     | 0                     |

| 1           | x    | х              | x              | X              | x     | x              | 1     | 1     | 1                     |

| $x \in \{0$ | ),1} |                |                |                |       |                |       |       |                       |

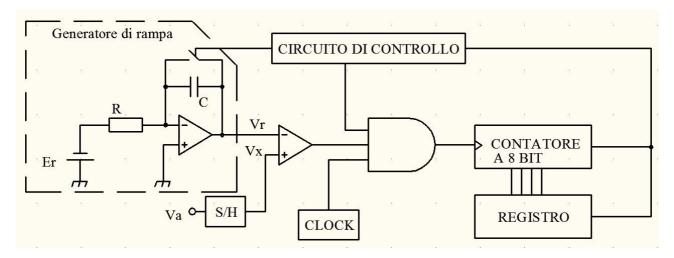

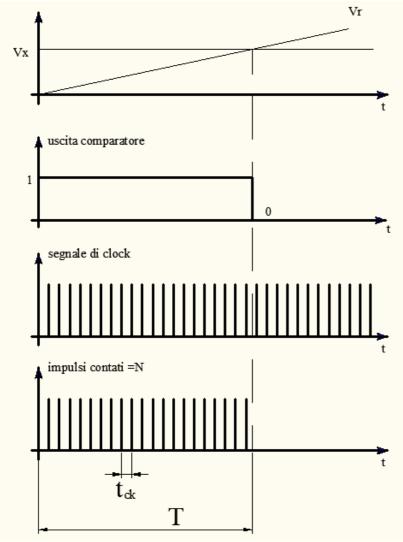

## CONVERTITORE A RAMPA SEMPLICE

$$V_r(t) = Kt$$

$V_r(T) = V_x = KT = KNt_{ck}$

$$V_x = \frac{K}{f_{ck}}N$$

I l segnale analogico Va arriva al circuito Sample & Hold e viene campionato.

Il segnale campionato Vx viene confrontato con una tensione a rampa Vr che viene dal generatore di rampa (un integratore con operazionale)

All'inizio della conversione la rampa è azzerata dal circuito di controllo e all'ingresso della porta AND arriva un uno dal circuito di controllo e un uno dal comparatore, quindi il segnale di clock arriva al contatore.

Fino a quando  $V_x > V_r$  il contatore conta, quando  $V_x < V_r$  il comparatore darà zero in uscita e chiude la porta al segnale di clock, il contatore smette di contare.

Risulta evidente che più è grande Vx maggiore è il tempo T in cui vengono contati gli impulsi a frequenza

$$f_{ck} = \frac{1}{t_{ck}}$$

e maggiore sarà il numero di impulsi contati N

$$N = \frac{T}{t_{ck}} = Tf_{ck}$$

questa ultima relazione ci dice che possiamo ottenere  $V_x$  direttamente proporzionale a un numero, ovvero  $V_x$  come multiplo intero del quanto  $\frac{K}{f_{ck}}$

Il registro memorizza il conteggio alla fine della conversione e lo mantiene fino alla fine della conversione successiva.

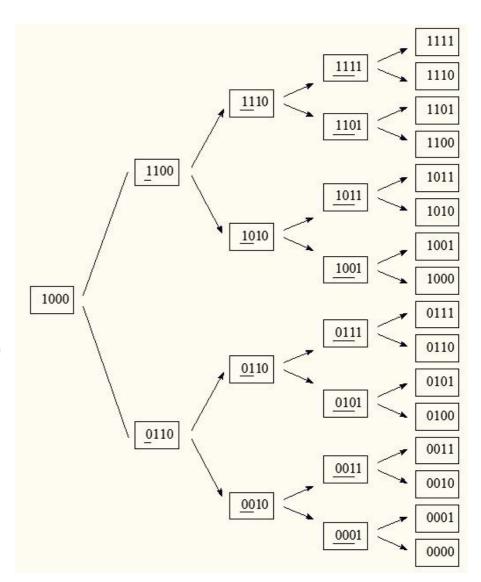

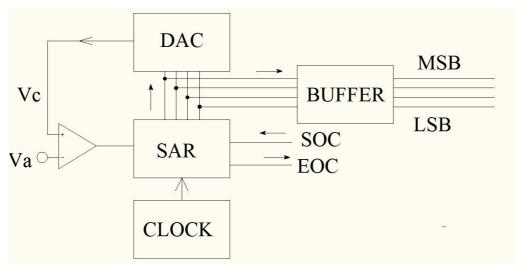

Un ADC ad approssimazioni **successive** (SAR - Successive Approximation Register) usa un comparatore e un convertitore digitaleanalogico, ad ogni passaggio l'ADC prova a impostare un bit, partendo dal MSB (Most Significant Bit, bit con peso maggiore) e usando il DAC confronta il segnale campionato con il segnale di ingresso in feedback. Questo convertitore individua un bit ad ogni iterazione in una sorta di ricerca binaria e la risoluzione è limitata solo dalle esigenze di sample-rate e dal rumore in ingresso.

# **CONVERTITORE DIGITALE ANALOGICO**

Il **Digital** (to) Analog Converter (DAC), in italiano Convertitore digitale-analogico, è un componente elettronico in grado di produrre sul suo terminale di uscita, un determinato livello di tensione o di corrente, in funzione di un valore numerico che viene presentato al suo ingresso; ad esempio, ad un valore pari ad 1 corrisponderà una tensione di uscita di 0,1V, ad un valore di 2 avremo 0,2V così via. La tabella di conversione dal valore digitale a quello analogico prende il nome di LUT (Look-Up Table) e può avere caratteristiche proporzionali (come nel precedente esempio), o può seguire un andamento del tutto arbitrario, a seconda del suo impiego.

Una larga diffusione ad uso domestico dei DAC si ha nei riproduttori digitali di suoni, nel controllo dell'apertura del diaframma nelle macchine fotografiche, nei controlli digitali (volume, luminosità) dei televisori e in tutte quelle situazioni nelle quali un'informazione numerica deve controllare una grandezza di tipo analogico.

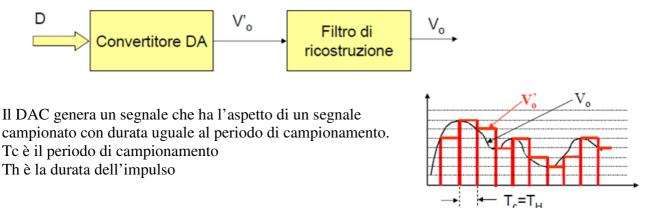

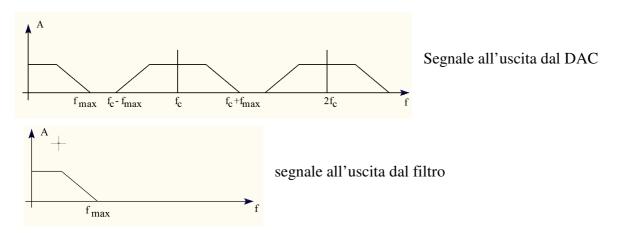

Il filtro di ricostruzione, passa basso, isola lo spettro in banda base

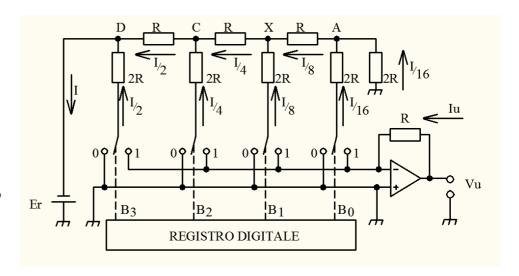

# CONVERTIRORE DIGITALE ANALOGICO R-2R A SCALA INVERTITA

Il numero digitale  $B_3B_2B_1B_0$  viene convertito in una tensione ottenuta dalla somma di quattro tensioni.

I bit comandano dei deviatori elettronici che collegano le resistenze 2R o a massa reale (ingresso + dell'operazionale) o a massa virtuale (all'ingresso – consideriamo il principio di massa virtuale).

La corrente Iu sarà

$$I_u = B_3 \frac{I}{2} + B_2 \frac{I}{4} + B_1 \frac{I}{8} + B_0 \frac{I}{16}$$

La rete R-2R ci permette di calcolare facilmente

$$I = \frac{E_r}{R}$$

La tensione di uscita Vu sarà

$$V_u = RI_u = R(B_3 \frac{\frac{E_r}{R}}{2} + B_2 \frac{\frac{E_r}{R}}{4} + B_1 \frac{\frac{E_r}{R}}{8} + B_0 \frac{\frac{E_r}{R}}{16})$$

$$V_u = E_r(B_3 \frac{1}{2} + B_2 \frac{1}{4} + B_1 \frac{1}{8} + B_0 \frac{1}{16})$$

$$V_u = \frac{E_r}{16} (8B_3 + 4B_2 + 2B_1 + B_0)$$

Quindi la Vu sarà in ogni istante un multiplo intero di  $\frac{E_r}{16}$  che è il quanto di questo convertitore.

Le definizioni di valore di fondo scala, valore max e quanto sono simili a quelle di un convertitore ADC

$$Q = \frac{V_{fs}}{2^N}$$

$V_{max} = V_{fs} - Q$  N = numero di bit

Nel nostro convertitore

$$Q = \frac{E_r}{16}$$

$N = 4$   $V_{fs} = 16Q$   $V_{max} = 15Q$